## **STMicroelectronics**

# ST31H320 A01 including optional cryptographic library NESLIB Security Target for composition

Common Criteria for IT security evaluation

SMD\_ST31H320\_ST\_14\_002 Rev A01.5

December 2015

## ST31H320 A01 platform Security Target for composition

## Common Criteria for IT security evaluation

## 1 Introduction (ASE\_INT)

## 1.1 Security Target reference

- Document identification: ST31H320 A01 including optional cryptographic library Neslib SECURITY TARGET FOR COMPOSITION.

- Version number: Rev A01.5, issued December 2015.

- 3 Registration: registered at ST Microelectronics under number

SMD\_ST31H320\_ST\_14\_002.

## 1.2 TOE reference

- This document presents **the Security Target for composition (ST)** of the **ST31H320 A01** Security Integrated Circuit (IC), designed on the **ST31 platform of STMicroelectronics**, with firmware version 2.0.2, and optional cryptographic library **Neslib 4.2.10**.

- The precise reference of the Target of Evaluation (TOE) is given in Section 1.4: TOE identification and the security IC features are given in Section 1.6: TOE description.

- A glossary of terms and abbreviations used in this document is given in *Appendix A: Glossary*.

## **Contents**

| 1    | Intro                                 | duction   | ո (ASE_INT)                        | 3             |  |  |  |

|------|---------------------------------------|-----------|------------------------------------|---------------|--|--|--|

|      | 1.1                                   | Securi    | ity Target reference               | 3             |  |  |  |

|      | 1.2                                   | TOE re    | eference                           | 3             |  |  |  |

|      | 1.3                                   | Conte     | Context                            |               |  |  |  |

|      | 1.4                                   | TOE ic    | dentification                      | 10            |  |  |  |

|      | 1.5                                   | TOE o     | verview                            | 11            |  |  |  |

|      | 1.6                                   | TOE d     | lescription                        | 12            |  |  |  |

|      |                                       | 1.6.1     | TOE hardware description           | 12            |  |  |  |

|      |                                       | 1.6.2     | TOE software description           | 13            |  |  |  |

|      |                                       | 1.6.3     | TOE documentation                  | 14            |  |  |  |

|      | 1.7                                   | TOE li    | fe cycle                           | 14            |  |  |  |

|      | 1.8                                   | TOE e     | environment                        | 15            |  |  |  |

|      |                                       | 1.8.1     | TOE Development Environment        | 15            |  |  |  |

|      |                                       | 1.8.2     | TOE production environment         | 16            |  |  |  |

|      |                                       | 1.8.3     | TOE operational environment        | 16            |  |  |  |

| 2    | Conformance claims (ASE_CCL, ASE_ECD) |           |                                    |               |  |  |  |

|      | 2.1                                   | Comm      | non Criteria conformance claims    | 18            |  |  |  |

|      | 2.2                                   | PP Cla    | aims                               | 18            |  |  |  |

|      |                                       | 2.2.1     | PP Reference                       | 18            |  |  |  |

|      |                                       | 2.2.2     | PP Additions                       | 18            |  |  |  |

|      |                                       | 2.2.3     | PP Claims rationale                | 19            |  |  |  |

| 3    | Seci                                  | urity pro | oblem definition (ASE_SPD)         | 20            |  |  |  |

|      | 3.1                                   | Descri    | iption of assets                   | 20            |  |  |  |

|      | 3.2                                   | Threat    | ts:                                | 22            |  |  |  |

|      | 3.3                                   | Organ     | isational security policies        | 22            |  |  |  |

|      | 3.4                                   | Assum     | nptions                            | 24            |  |  |  |

| 4    | Seci                                  | urity obj | jectives (ASE_OBJ)                 | 25            |  |  |  |

|      | 4.1                                   | Securi    | ity objectives for the TOE         | 25            |  |  |  |

|      | 4.2                                   | Securi    | ity objectives for the environment | 26            |  |  |  |

|      | 4.3                                   |           | ity objectives rationale           |               |  |  |  |

| 1/00 |                                       |           | OMD 070411000 07 44 000            | <del>,,</del> |  |  |  |

|   |      | 4.3.1     | TOE threat "Memory Access Violation"                                                                                                                       | . 28 |

|---|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   |      | 4.3.2     | Organisational security policy "Additional Specific Security Functionali                                                                                   |      |

|   |      | 4.3.3     | Organisational security policy "Controlled loading of the Security IC Embedded Software"                                                                   |      |

| 5 | Secu | ırity rec | րuirements (ASE_REQ)                                                                                                                                       | . 30 |

|   | 5.1  | Securi    | ty functional requirements for the TOE                                                                                                                     | . 30 |

|   |      | 5.1.1     | Security Functional Requirements from the Protection Profile                                                                                               | . 32 |

|   |      | 5.1.2     | Additional Security Functional Requirements for the cryptographic services                                                                                 | 34   |

|   |      | 5.1.3     | Additional Security Functional Requirements for the memories protect                                                                                       |      |

|   |      | 5.1.4     | Additional Security Functional Requirements related to the possible availability of final test and loading capabilities in phases 4 to 6 of the life-cycle |      |

|   | 5.2  | TOE s     | ecurity assurance requirements                                                                                                                             | . 40 |

|   | 5.3  | Refine    | ment of the security assurance requirements                                                                                                                | . 41 |

|   |      | 5.3.1     | Refinement regarding functional specification (ADV_FSP)                                                                                                    | . 42 |

|   |      | 5.3.2     | Refinement regarding test coverage (ATE_COV)                                                                                                               | . 43 |

|   | 5.4  | Securi    | ty Requirements rationale                                                                                                                                  | . 43 |

|   |      | 5.4.1     | Rationale for the Security Functional Requirements                                                                                                         | . 43 |

|   |      | 5.4.2     | Additional security objectives are suitably addressed                                                                                                      |      |

|   |      | 5.4.3     | Additional security requirements are consistent                                                                                                            | . 47 |

|   |      | 5.4.4     | "Dependencies of Security Functional Requirements                                                                                                          | . 47 |

|   |      | 5.4.5     | Rationale for the Assurance Requirements                                                                                                                   | . 50 |

| 6 | TOE  | summa     | ary specification (ASE_TSS)                                                                                                                                | . 51 |

|   | 6.1  | Limited   | d fault tolerance (FRU_FLT.2)                                                                                                                              | . 51 |

|   | 6.2  | Failure   | e with preservation of secure state (FPT_FLS.1)                                                                                                            | . 51 |

|   | 6.3  | Limited   | d capabilities (FMT_LIM.1) / Test                                                                                                                          | . 51 |

|   | 6.4  | Limited   | d capabilities (FMT_LIM.1) / Loader                                                                                                                        | . 51 |

|   | 6.5  | Limited   | d availability (FMT_LIM.2) / Test & (FMT_LIM.2) / Loader                                                                                                   | . 51 |

|   | 6.6  |           | data confidentiality (FDP_SDC.1)                                                                                                                           |      |

|   | 6.7  |           | data integrity monitoring and action (FDP_SDI.2)                                                                                                           |      |

|   | 6.8  |           | storage (FAU_SAS.1)                                                                                                                                        |      |

|   | 6.9  |           | ance to physical attack (FPT_PHP.3)                                                                                                                        |      |

|   | 0.9  | LG212[    | ande to physical attack (FF 1_F11F.3)                                                                                                                      | . 52 |

|        | 6.10    | Basic internal transfer protection (FDP_ITT.1), Basic internal TSF data transfer protection (FPT_ITT.1) & Subset information flow control (FDP_IFC.1) 52                                      |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 6.11    | Random number generation (FCS_RNG.1)                                                                                                                                                          |

|        | 6.12    | Cryptographic operation: EDES operation (FCS_COP.1) / EDES 52                                                                                                                                 |

|        | 6.13    | Cryptographic operation: AES operation (FCS_COP.1) / AES                                                                                                                                      |

|        | 6.14    | Cryptographic operation: RSA operation (FCS_COP.1) / RSA if Neslib only                                                                                                                       |

|        | 6.15    | Cryptographic operation: Elliptic Curves Cryptography operation (FCS_COP.1) / ECC if Neslib only                                                                                              |

|        | 6.16    | Cryptographic operation: SHA operation (FCS_COP.1) / SHA, if Neslib only                                                                                                                      |

|        | 6.17    | Cryptographic operation: DRBG operation (FCS_COP.1) / DRBG, if Neslib only                                                                                                                    |

|        | 6.18    | Cryptographic key generation: Prime generation (FCS_CKM.1) / Prime_generation, if Neslib only                                                                                                 |

|        | 6.19    | Cryptographic key generation: RSA key generation (FCS_CKM.1) / RSA_key_generation, if Neslib only                                                                                             |

|        | 6.20    | Static attribute initialisation (FMT_MSA.3) / Memories                                                                                                                                        |

|        | 6.21    | Management of security attributes (FMT_MSA.1) / Memories & Specification of management functions (FMT_SMF.1) / Memories                                                                       |

|        | 6.22    | Complete access control (FDP_ACC.2) / Memories & Security attribute based access control (FDP_ACF.1) / Memories                                                                               |

|        | 6.23    | Static attribute initialisation (FMT_MSA.3) / Loader                                                                                                                                          |

|        | 6.24    | Management of security attributes (FMT_MSA.1) / Loader & Specification of management functions (FMT_SMF.1) / Loader                                                                           |

|        | 6.25    | Subset access control (FDP_ACC.1) / Loader, Security attribute based access control (FDP_ACF.1) / Loader, Security roles (FMT_SMR.1) / Loader & Timing of identification (FIA_UID.1) / Loader |

|        | 6.26    | Import of user data without security attributes (FDP_ITC.1) / Loader 55                                                                                                                       |

| 7      | ldent   | ification                                                                                                                                                                                     |

| 8      | Refe    | rences                                                                                                                                                                                        |

| Append | lix A G | Glossary                                                                                                                                                                                      |

|        | A.1     | Terms                                                                                                                                                                                         |

|        | A.2     | Abbreviations                                                                                                                                                                                 |

| ST31H320 A0 | 1 platform | Security | <b>Target</b> |

|-------------|------------|----------|---------------|

|-------------|------------|----------|---------------|

| _ |    |   |    |   |      |

|---|----|---|----|---|------|

| _ | _  | - | +~ | - | +-   |

|   | L) |   | te | ш | 11.5 |

| 9 | Revision history | <br>. 67 |

|---|------------------|----------|

## List of tables

| Table 1.  | TOE components                                              | . 10 |

|-----------|-------------------------------------------------------------|------|

| Table 2.  | Derivative devices configuration possibilities              | . 11 |

| Table 3.  | Composite product life cycle phases                         | . 15 |

| Table 4.  | Summary of security aspects                                 | . 20 |

| Table 5.  | Summary of security objectives                              | . 25 |

| Table 6.  | Security Objectives versus Assumptions, Threats or Policies | . 27 |

| Table 7.  | Summary of functional security requirements for the TOE     | . 30 |

| Table 8.  | FCS_COP.1 iterations (cryptographic operations)             | . 35 |

| Table 9.  | FCS_CKM.1 iterations (cryptographic key generation)         | . 37 |

| Table 10. | TOE security assurance requirements                         | . 41 |

| Table 11. | Impact of EAL5 selection on BSI-CC-PP-0084-2014 refinements | . 42 |

| Table 12. | Security Requirements versus Security Objectives            | . 44 |

| Table 13. | Dependencies of security functional requirements            | . 47 |

| Table 14. | TOE components                                              | . 56 |

| Table 15. | Guidance documentation                                      | . 56 |

| Table 16. | Sites list                                                  | . 57 |

| Table 17. | Common Criteria                                             | . 60 |

| Table 18. | Protection Profile                                          | . 60 |

| Table 19. | Other standards                                             | . 60 |

| Table 20. | List of abbreviations                                       | . 65 |

| Table 21. | Document revision history                                   | . 67 |

# List of figures

| Figure 1. | ST31H320 A01 | olatform block diagram | 13 |

|-----------|--------------|------------------------|----|

|           |              |                        |    |

## 1.3 Context

- The Target of Evaluation (TOE) referred to in *Section 1.4: TOE identification*, is evaluated under the French IT Security Evaluation and Certification Scheme and is developed by the Secure Microcontrollers Division of STMicroelectronics (ST).

- The assurance level of the performed Common Criteria (CC) IT Security Evaluation is EAL5 augmented by ADV\_IMP.2, ADV\_INT.3, ADV\_TDS.5, ALC\_CMC.5, ALC\_DVS.2, ALC\_FLR.1, ALC\_TAT.3, ATE\_COV.3, ATE\_FUN.2 and AVA\_VAN.5.

- The intent of this Security Target is to specify the Security Functional Requirements (SFRs) and Security Assurance Requirements (SARs) applicable to the TOE security ICs, and to summarise their chosen TSF services and assurance measures.

- This ST claims to be an instantiation of the "Eurosmart Security IC Platform Protection Profile with Augmentation Packages" (PP) registered and certified under the reference BSI-CC-PP-0084-2014 in the German IT Security Evaluation and Certification Scheme, with the following augmentations:

Addition #1: "Support of Cipher Schemes" from AUG

Addition #4: "Area based Memory Access Control" from AUG

Additions specific to this Security Target.

The original text of this PP is typeset as indicated here, its augmentations from *AUG* as indicated here, when they are reproduced in this document.

This ST also instantiates the following package from the above mentioned PP:

- Loader dedicated for usage in secured environment only.

- Extensions introduced in this ST to the SFRs of the Protection Profile (PP) are **exclusively** drawn from the Common Criteria part 2 standard SFRs.

- This ST makes various refinements to the above mentioned PP and *AUG*. They are all properly identified in the text typeset as *indicated here*. The original text of the PP is repeated as scarcely as possible in this document for reading convenience. All PP identifiers have been however prefixed by their respective origin label: *BSI* for *BSI-CC-PP-0084-2014*, *AUG1* for Addition #1 of *AUG* and *AUG4* for Addition #4 of *AUG*.

## 1.4 TOE identification

- The Target of Evaluation (TOE) is the ST31H320 A01 platform.

- "ST31H320 A01" completely identifies the TOE including its components listed in *Table 1:*\*\*TOE components, its guidance documentation detailed in *Table 15: Guidance documentation*, and its development and production sites indicated in *Table 16: Sites list*.

- A01 is the version of the evaluated platform. Any change in the TOE components, the guidance documentation and the list of sites leads to a new version of the evaluated platform, thus a new TOE.

Table 1. TOE components

| IC Maskset name | IC<br>version | Master<br>identification<br>number <sup>(1)</sup> | Firmware version | OST<br>version | Optional Neslib<br>crypto library<br>version |

|-----------------|---------------|---------------------------------------------------|------------------|----------------|----------------------------------------------|

| K8N0A           | С             | 00DE                                              | 2.0.2            | 4.0            | 4.2.10                                       |

- 1. Part of the product information.

- The IC maskset name is the product hardware identification.

The IC version is updated for any change in hardware (i.e. part of the layers of the maskset) or in the OST software.

- All along the product life, the marking on the die, a set of accessible registers and a set of specific instructions allow the customer to check the product information, providing the identification elements, as listed in *Table 1: TOE components*, and the configuration elements as detailed in the Data Sheet, referenced in *Table 15: Guidance documentation*.

## 1.5 TOE overview

- Designed for secure ID and banking applications, the TOE is a serial access microcontroller that incorporates the most recent generation of ARM® processors for embedded secure systems. Its SecurCore® SC000™ 32-bit RISC core is built on the Cortex™ M0 core with additional security features to help to protect against advanced forms of attacks.

- 19 Different derivative devices may be configured depending on the customer needs:

- either by ST during the manufacturing or packaging process,

- or by the customer during the packaging, or composite product integration, or personnalisation process.

- They all share the same hardware design and the same maskset (denoted by the Master identification number). The Master identification number is unique for all product configurations.

- The configuration of the derivative devices can impact the available NVM size, and he availability of Nescrypt as detailed here below:

Table 2. Derivative devices configuration possibilities

| Features | Possible values              |

|----------|------------------------------|

| NVM size | 128, 192, 256, or 320 Kbytes |

| Nescrypt | Active, Inactive             |

- All combinations of different features values are possible and covered by this certification.

All possible configurations can vary under a unique IC, and without impact on security.

- The Master identification number is unique for all product configurations.

Each derivative device has a specific Child product identification number, also part of the product information, and specified in the Data Sheet and in the Firmware User Manual, referenced in *Table 15*.

- The rest of this document applies to all possible configurations of the TOE, with or without Neslib, except when a restriction is mentioned. For easier reading, the restrictions are typeset as indicated here.

- In a few words, the ST31H320 A01 offers a unique combination of high performances and very powerful features for high level security:

- · Die integrity,

- Monitoring of environmental parameters,

- · Protection mechanisms against faults,

- AIS20/AIS31 class PTG.2 compliant True Random Number Generator,

- Hardware Security Enhanced DES accelerator,

- Hardware Security AES accelerator,

- ISO 3309 CRC calculation block,

- Memory Protection Unit,

- optional NExt Step CRYPTography accelerator (NESCRYPT),

- · optional cryptographic library.

## 1.6 TOE description

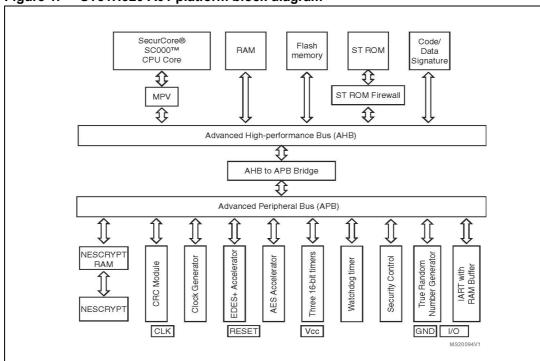

## 1.6.1 TOE hardware description

- The TOE features hardware accelerators for advanced cryptographic functions, with built-in countermeasures against side channel attacks. The AES (Advanced Encryption Standard) accelerator provides a high-performance implementation of AES-128, AES-192 and AES-256 algorithms. The 3-key triple DES accelerator (EDES+) supports efficiently the Data Encryption Standard (TDES [2]), enabling Cipher Block Chaining (CBC) mode and triple DES computation. If Nescrypt is active, the NESCRYPT crypto-processor allows fast and secure implementation of the most popular public key cryptosystems with a high level of performance ([7], [9], [12],[13], [14], [15]).

- The TOE offers 10 Kbytes of User RAM and up to 320 Kbytes of secure User high-density Flash memory (NVM).

- As randomness is a key stone in many applications, the ST31H320 A01 features a highly reliable True Random Number Generator (TRNG), compliant with PTG.2 Class of AIS20/AIS31 [1] and directly accessible thru dedicated registers.

- This device also includes the ARM® SecurCore® SC000™ memory protection unit (MPU), which enables the user to define its own region organization with specific protection and access permissions.

- The TOE offers a contact serial communication interface fully compatible with the ISO/IEC 7816-3 standard.

- The detailed features of this TOE are described in the Data Sheet and in the Cortex SC000 Technical Reference Manual, referenced in *Table 15*.

- 32 Figure 1 provides an overview of the ST31H320 A01 platform.

Figure 1. ST31H320 A01 platform block diagram

## 1.6.2 TOE software description

- The OST ROM contains a Dedicated Software which provides full test capabilities (operating system for test, called "OST"), not accessible by the Security IC Embedded Software (ES), after TOE delivery.

- The System ROM and ST NVM of the TOE contain a Dedicated Software which provides a very reduced set of commands for final test (operating system for final test, called "FTOS"), not intended for the Security IC Embedded Software (ES) usage, and not available in User configuration.

- The System ROM and ST NVM of the TOE contain a Dedicated Support Software called Secure Flash Loader, enabling to securely and efficiently download the Security IC Embedded Software (ES) into the NVM. It also allows the evaluator to load software into the TOE for test purpose. The Secure Flash Loader is not available in User configuration.

- The System ROM and ST NVM of the TOE contain a Dedicated Support Software, which provides low-level functions (called Flash Drivers), enabling the Security IC Embedded Software (ES) to modify and manage the NVM contents. The Flash Drivers are available all through the product life-cycle.

- 37 The Security IC Embedded Software (ES) is in User NVM.

**Note**: The ES is not part of the TOE and is out of scope of the evaluation, except Neslib, when it is embedded.

The TOE optionally comprises a specific application in User NVM: this applicative Embedded Software is a cryptographic library called Neslib. Neslib is a cutting edge cryptographic library in terms of security and performance. Neslib is embedded by the ES developer in his applicative code. Note that Neslib can only be used if Nescrypt is active.

NesLib is a cryptographic toolbox supporting the most common standards and protocols:

- an asymmetric key cryptographic support module, supporting secure modular arithmetic with large integers, with specialized functions for Rivest, Shamir & Adleman Standard cryptographic algorithm (RSA [14]),

- an asymmetric key cryptographic support module that provides very efficient basic functions to build up protocols using Elliptic Curves Cryptography on prime fields GF(p) [12], and provides support for ECDH key agreement [19] and ECDSA generation and verification [5].

- a cryptographic support module that provides secure hash functions (SHA-1<sup>(a)</sup>, SHA-224, SHA-256, SHA-384, and SHA-512 [4]),

- support for Deterministic Random Bit Generators [17],

- prime number generation and RSA key pairs generation [3].

#### 1.6.3 **TOE** documentation

- 39 The user guidance documentation, part of the TOE, consists of:

- the product Data Sheet and die description,

- the product family Security Guidance,

- the AIS31 user manuals,

- the product family programming manual,

- the ARM SC000 Technical Reference Manual.

- the Firmware user manual.

- the Flash loader installation guide,

- optionally the Neslib user manual.

- 40 The complete list of guidance documents is detailed in *Table 15*.

#### 1.7 **TOE life cycle**

- This Security Target is fully conform to the claimed PP. In the following, just a summary and 41 some useful explanations are given. For complete details on the TOE life cycle, please refer to the Eurosmart - Security IC Platform Protection Profile with Augmentation Packages (BSI-CC-PP-0084-2014), section 1.2.3.

- 42 The composite product life cycle is decomposed into 7 phases. Each of these phases has the very same boundaries as those defined in the claimed protection profile.

- 43 The life cycle phases are summarized in *Table 3*.

- 44 The sites potentially involved in the TOE life cycle are listed in *Table 16*.

- 45 The limit of the evaluation corresponds to phases 2, 3 and optionally 4, including the delivery and verification procedures of phase 1, and the TOE delivery either to the IC

Note that SHA-1 is no longer recommended as a cryptographic function in the context of smart card applications. Hence, Security IC Embedded Software may need to use another SHA to achieve a suitable

packaging manufacturer or to the composite product integrator; procedures corresponding to phases 1, 5, 6 and 7 are outside the scope of this evaluation.

- In the following, the term "Composite product manufacturing" is uniquely used to indicate phases 1, optionally 4, 5 and 6 all together.

- This ST also uses the term "Composite product manufacturer" which includes all roles responsible of the TOE during phases 1, optionally 4, 5 and 6.

- The TOE is delivered after Phase 3 in form of wafers or after Phase 4 in packaged form, depending on the customer's order.

- In the following, the term "TOE delivery" is uniquely used to indicate:

- after Phase 3 (or before Phase 4) if the TOE is delivered in form of wafers or sawn wafers (dice) or

- after Phase 4 (or before Phase 5) if the TOE is delivered in form of packaged products.

- The TOE is delivered in User or Admin configuration.

Table 3. Composite product life cycle phases

| Phase | Name                                      | Description                                                                                    |

|-------|-------------------------------------------|------------------------------------------------------------------------------------------------|

| 1     | Security IC embedded software development | security IC embedded software development specification of IC pre-personalization requirements |

| 2     | IC development                            | IC design IC dedicated software development                                                    |

| 3     | IC manufacturing and testing              | integration and photomask fabrication IC manufacturing IC testing IC pre-personalisation       |

| 4     | IC packaging                              | security IC packaging (and testing) pre-personalisation if necessary                           |

| 5     | Security IC product finishing process     | composite product finishing process composite product testing                                  |

| 6     | Security IC personalisation               | composite product personalisation composite product testing                                    |

| 7     | Security IC end usage                     | composite product usage by its issuers and consumers                                           |

## 1.8 TOE environment

- 50 Considering the TOE, three types of environments are defined:

- Development environment corresponding to phase 2,

- Production environment corresponding to phase 3 and optionally 4,

- Operational environment, including phase 1 and from phase 4 or 5 to phase 7.

## 1.8.1 TOE Development Environment

To ensure security, the environment in which the development takes place is secured with controllable accesses having traceability. Furthermore, all authorised personnel involved

fully understand the importance and the strict implementation of defined security procedures.

- The development begins with the TOE's specification. All parties in contact with sensitive information are required to abide by Non-Disclosure Agreements.

- Design and development of the IC then follows, together with the dedicated and engineering software and tools development. The engineers use secure computer systems (preventing unauthorised access) to make their developments, simulations, verifications and generation of the TOE's databases. Sensitive documents, files and tools, databases on tapes, and printed circuit layout information are stored in appropriate locked cupboards/safe. Of paramount importance also is the disposal of unwanted data (complete electronic erasures) and documents (e.g. shredding).

- The development centres possibly involved in the development of the TOE are denoted by the activity "DEV" in *Table 16*.

- Reticules and photomasks are generated from the verified IC databases; the former are used in the silicon Wafer-fab processing. As reticules and photomasks are generated off-site, they are transported and worked on in a secure environment. During the transfer of sensitive data electronically, procedures are established to ensure that the data arrive only at the destination and are not accessible at intermediate stages (e.g. stored on a buffer server where system administrators make backup copies).

- The authorized sub-contractors potentially involved in the TOE mask manufacturing are denoted by the activity "MASK" in *Table 16*.

### 1.8.2 TOE production environment

- As high volumes of product commonly go through such environments, adequate control procedures are necessary to account for all product at all stages of production.

- Production starts within the Wafer-fab; here the silicon wafers undergo the diffusion processing. Computer tracking at wafer level throughout the process is commonplace. The wafers are then taken into the test area. Testing of each TOE occurs to assure conformance with the device specification.

- The authorized front-end plant possibly involved in the manufacturing of the TOE are denoted by the activity "FE" in *Table 16*.

- The authorized EWS plant potentially involved in the testing of the TOE are denoted by the activity "EWS" in *Table 16*.

- Wafers are then scribed and broken such as to separate the functional from the nonfunctional ICs. The latter is discarded in a controlled accountable manner. The good ICs are then packaged in phase 4, in a back-end plant. When testing, programming or deliveries are done offsite, ICs are transported and worked on in a secure environment with accountability and traceability of all (good and bad) products.

- When the product is delivered after phase 4, the authorized back-end plants possibly involved in the packaging of the TOE are denoted by the activity "BE" in *Table 16*.

- All sites are denoted by the activity "WHS" in *Table 16* can be involved for the logistics.

#### 1.8.3 TOE operational environment

- A TOE operational environment is the environment of phases 1, optionally 4, then 5 to 7.

- 65 At phases 1, 4, 5 and 6, the TOE operational environment is a controlled environment.

End-user environments (phase 7): composite products are used in a wide range of applications to assure authorised conditional access. Examples of such are pay-TV, banking cards, brand protection, portable communication SIM cards, health cards, transportation cards, access management, identity and passport cards. The end-user environment therefore covers a wide range of very different functions, thus making it difficult to avoid and monitor any abuse of the TOE.

## 2 Conformance claims (ASE CCL, ASE ECD)

## 2.1 Common Criteria conformance claims

- The ST31H320 A01 platform Security Target claims to be conformant to the Common Criteria version 3.1 revision 4.

- Furthermore it claims to be CC Part 2 (CCMB-2012-09-002 R4) extended and CC Part 3 (CCMB-2012-09-003 R4) conformant.

- The extended Security Functional Requirements are those defined in the *Eurosmart* Security IC Platform Protection Profile with Augmentation Packages (BSI-CC-PP-0084-2014):

- FCS\_RNG Generation of random numbers,

- FMT\_LIM Limited capabilities and availability,

- FAU\_SAS Audit data storage,

- FDP\_SDC Stored data confidentiality.

The reader can find their certified definitions in the text of the "BSI-CC-PP-0084-2014" Protection Profile.

The assurance level for the ST31H320 A01 platform Security Target is *EAL5* augmented by ADV\_IMP.2, ADV\_INT.3, ADV\_TDS.5, ALC\_CMC.5, ALC\_DVS.2, ALC\_FLR.1, ALC\_TAT.3, ATE\_COV.3, ATE\_FUN.2 and AVA\_VAN.5.

## 2.2 PP Claims

#### 2.2.1 PP Reference

71 The ST31H320 A01 platform Security Target claims strict conformance to the *Eurosmart* - Security IC Platform Protection Profile with Augmentation Packages (BSI-CC-PP-0084-2014), for the part of the TOE covered by this PP (Security IC), as required by this Protection Profile.

#### 2.2.2 PP Additions

- The main additions operated on the *BSI-CC-PP-0084-2014* are:

- Addition #4: "Area based Memory Access Control" from AUG,

- Addition #1: "Support of Cipher Schemes" from AUG,

- Specific additions for the Secure Flash Loader

- Refinement of assurance requirements.

- All refinements are indicated with type setting text **as indicated here**, original text from the **BSI-CC-PP-0084-2014** being typeset as indicated here. Text originating in **AUG** is typeset as indicated here.

- 74 The security environment additions relative to the PP are summarized in *Table 4*.

- The additional security objectives relative to the PP are summarized in *Table 5*.

- A simplified presentation of the TOE Security Policy (TSP) is added.

- 77 The additional SFRs for the TOE relative to the PP are summarized in *Table 7*.

78 The additional SARs relative to the PP are summarized in *Table 10*.

#### 2.2.3 PP Claims rationale

- The differences between this Security Target security objectives and requirements and those of *BSI-CC-PP-0084-2014*, to which conformance is claimed, have been identified and justified in *Section 4* and in *Section 5*. They have been recalled in the previous section.

- In the following, the statements of the security problem definition, the security objectives, and the security requirements are consistent with those of the *BSI-CC-PP-0084-2014*.

- The security problem definition presented in Section 3, clearly shows the additions to the security problem statement of the PP.

- The security objectives rationale presented in *Section 4.3* clearly identifies modifications and additions made to the rationale presented in the *BSI-CC-PP-0084-2014*.

- Similarly, the security requirements rationale presented in *Section 5.4* has been updated with respect to the protection profile.

- All PP requirements have been shown to be satisfied in the extended set of requirements whose completeness, consistency and soundness have been argued in the rationale sections of the present document.

## 3 Security problem definition (ASE\_SPD)

- This section describes the security aspects of the environment in which the TOE is intended to be used and addresses the description of the assets to be protected, the threats, the organisational security policies and the assumptions.

- Note that the origin of each security aspect is clearly identified in the prefix of its label. Most of these security aspects can therefore be easily found in the *Eurosmart Security IC Platform Protection Profile with Augmentation Packages* (*BSI-CC-PP-0084-2014*), section 3. Only those originating in *AUG*, and the ones introduced in this Security Target, are detailed in the following sections.

- A summary of all these security aspects and their respective conditions is provided in *Table 4*.

88 Table 4. Summary of security aspects

|             | Label                   | Title                                                              |

|-------------|-------------------------|--------------------------------------------------------------------|

|             | BSI.T.Leak-Inherent     | Inherent Information Leakage                                       |

|             | BSI.T.Phys-Probing      | Physical Probing                                                   |

| ats         | BSI.T.Malfunction       | Malfunction due to Environmental Stress                            |

| threats     | BSI.T.Phys-Manipulation | Physical Manipulation                                              |

| TOE t       | BSI.T.Leak-Forced       | Forced Information Leakage                                         |

| 12          | BSI.T.Abuse-Func        | Abuse of Functionality                                             |

|             | BSI.T.RND               | Deficiency of Random Numbers                                       |

|             | AUG4.T.Mem-Access       | Memory Access Violation                                            |

|             | BSI.P.Process-TOE       | Protection during TOE Development and Production                   |

|             | BSI.P.Lim_Block_Loader  | Limiting and blocking the loader functionality                     |

| OSPs        | AUG1.P.Add-Functions    | Additional Specific Security Functionality (Cipher Scheme Support) |

|             | P.Controlled-ES-Loading | Controlled loading of the Security IC Embedded Software            |

|             | P.Resp-Appl             | Treatment of user data                                             |

| ptions      | BSI.A.Process-Sec-IC    | Protection during Packaging, Finishing and Personalisation         |

| Assumptions | BSI.A.Resp-Appl         | Treatment of User Data                                             |

## 3.1 Description of assets

Since this Security Target claims strict conformance to the *Eurosmart - Security IC Platform*Protection Profile with Augmentation Packages (BSI-CC-PP-0084-2014), the assets defined in section 3.1 of the Protection Profile are applied and the assets regarding threats are clarified in this Security Target.

- 90 The assets (related to standard functionality) to be protected are

- the user data of the Composite TOE,

- - the Security IC Embedded Software, stored and in operation,

- - the security services provided by the TOE for the Security IC Embedded Software.

- The user (consumer) of the TOE places value upon the assets related to high-level security concerns:

- SC1 integrity of user data of the Composite TOE,

- SC2 confidentiality of user data of the Composite TOE being stored in the TOE's protected memory areas,

- SC3 correct operation of the security services provided by the TOE for the Security IC Embedded Software.

- Note the Security IC Embedded Software is user data and shall be protected while being executed/processed and while being stored in the TOE's protected memories.

- According to this Protection Profile there is the following high-level security concern related to security service:

- SC4 deficiency of random numbers.

- To be able to protect these assets (SC1 to SC4) the TOE shall self-protect its TSF. Critical information about the TSF shall be protected by the development environment and the operational environment. Critical information may include:

- logical design data, physical design data, IC Dedicated Software, and configuration data.

- Initialisation Data and Pre-personalisation Data, specific development aids, test and characterisation related data, material for software development support, and photomasks.

- 95 Such information and the ability to perform manipulations assist in threatening the above assets.

- The information and material produced and/or processed by the TOE Manufacturer in the TOE development and production environment (Phases 2 up to TOE Delivery) can be grouped as follows:

- logical design data,

- physical design data,

- IC Dedicated Software, Initialisation Data and Pre-personalisation Data,

- Security IC Embedded Software, provided by the Security IC Embedded Software developer and implemented by the IC manufacturer,

- specific development aids.

- test and characterisation related data,

- material for software development support, and

- photomasks and products in any form

as long as they are generated, stored, or processed by the TOE Manufacturer.

97 Application note:

The TOE providing a functionality for Security IC Embedded Software secure loading into NVM, the ES is considered as User Data being stored in the TOE's memories at this step, and the Protection Profile security concerns are extended accordingly.

## 3.2 Threats

98 The threats are described in the *BSI-CC-PP-0084-2014*, section 3.2. Only those originating in *AUG* are detailed in the following section.

BSI.T.Leak-Inherent Inherent Information Leakage

BSI.T.Phys-Probing Physical Probing

BSI.T.Malfunction Malfunction due to Environmental Stress

BSI.T.Phys- Physical Manipulation

Manipulation

BSI.T.Leak-Forced Forced Information Leakage

BSI.T.Abuse-Func Abuse of Functionality

BSI.T.RND Deficiency of Random Numbers

AUG4.T.Mem-Access Memory Access Violation:

Parts of the **Security IC** Embedded Software may cause security violations by accidentally or deliberately accessing restricted data (which may include code). Any restrictions are defined by the security policy of the specific application context and must be implemented by the **Security IC** Embedded Software.

Clarification: This threat does not address the proper definition and management of the security rules implemented by the Security IC Embedded Software, this being a software design and correctness issue. This threat addresses the reliability of the abstract machine targeted by the software implementation. To avert the threat, the set of access rules provided by this TOE should be undefeated if operated according to the provided guidance. The threat is not realized if the Security IC Embedded Software is designed or implemented to grant access to restricted information. It is realized if an implemented access denial is granted under unexpected conditions or if the execution machinery does not effectively control a controlled access.

Here the attacker is expected to (i) take advantage of flaws in the design and/or the implementation of the TOE memory access rules (refer to BSI.T.Abuse-Func but for functions available after TOE delivery), (ii) introduce flaws by forcing operational conditions (refer to BSI.T.Malfunction) and/or by physical manipulation (refer to BSI.T.Phys-Manipulation). This attacker is expected to have a high level potential of attack.

## 3.3 Organisational security policies

The TOE provides specific security functionality that can be used by the **Security IC**Embedded Software. In the following specific security functionality is listed which is not derived from threats identified for the TOE's environment because it can only be decided in the context of the **Security IC** application, against which threats the **Security IC** Embedded Software will use the specific security functionality.

- ST applies the Protection policy during TOE Development and Production (*BSI.P.Process-TOE*) as specified below.

- 101 BSI.P.Lim\_Block\_Loader is dedicated to the Secure Flash Loader, and described in the BSI-CC-PP-0084-2014 package "Loader dedicated for usage in secured environment only".

- **ST** applies the Additional Specific Security Functionality policy (*AUG1.P.Add-Functions*) as specified below.

- New Organisational Security Policies (OSPs) are defined here below:

- P.Controlled-ES-Loading is related to the capability provided by the TOE to load Security IC Embedded Software into the NVM after TOE delivery, in a controlled manner, during composite product manufacturing. The use of this capability is optional, and depends on the customer's production organization.

- P.Resp-Appl is related to the ES that is part of the evaluation, and valid in case Neslib is embbeded in the TOE.

BSI.P.Process-TOE Identification during TOE Development and Production:

An accurate identification *is* established for the TOE. This requires that each instantiation of the TOE carries this unique identification.

BSI.P.Lim Block Loader Limiting and blocking the loader fuctionality:

The composite manufacturer uses the Loader for loading of Security IC Embedded Software, user data of the Composite Product or IC Dedicated Support Software in charge of the IC Manufacturer. He limits the capability and blocks the availability of the Loader in order to protect stored data from disclosure and manipulation.

AUG1.P.Add-Functions Additional Specific Security Functionality:

The TOE shall provide the following specific security functionality to the Security IC Embedded Software:

- Triple Data Encryption Standard (TDES),

- Advanced Encryption Standard (AES),

- Elliptic Curves Cryptography on GF(p), if Neslib is embedded only.

- Secure Hashing (SHA-1<sup>(1)</sup>, SHA-224, SHA-256, SHA-384, SHA-512), if Neslib is embedded only,

- Rivest-Shamir-Adleman (RSA), if Neslib is embedded only,

- Deterministic Random Bit Generator (DRBG), if Neslib is embedded only,

- Prime Number Generation, if Neslib is embedded only

- Note that SHA-1 is no longer recommended as a cryptographic function in the context of smart card applications. Hence, Security IC Embedded Software may need to use another SHA to achieve a suitable strength.

P.Controlled-ES-Loading Controlled loading of the Security IC Embedded Software:

The TOE shall provide the capability to import the Security IC Embedded Software into the NVM, in a controlled manner, either before TOE delivery, under ST authority, either after TOE delivery, under the composite product manufacturer authority.

This capability is not available in User configuration.

P.Resp-Appl Treatment of user data:

The Security IC Embedded Software, part of the TOE, treats user data according to the assumption A.Resp-Appl defined in BSI-

CC-PP-0084-2014.

## 3.4 Assumptions

The following assumptions are described in the BSI-CC-PP-0084-2014, section 3.4.

BSI.A.Process-Sec-IC Protection during Packaging, Finishing and Personalisation

BSI.A.Resp-Appl Treatment of User Data of the Composite TOE

## 4 Security objectives (ASE\_OBJ)

The security objectives of the TOE cover principally the following aspects:

- · integrity and confidentiality of assets,

- protection of the TOE and associated documentation during development and production phases,

- · provide random numbers,

- provide cryptographic support and access control functionality.

- 108 A summary of all security objectives is provided in *Table 5*.

- Note that the origin of each objective is clearly identified in the prefix of its label. Most of these security aspects can therefore be easily found in the *BSI-CC-PP-0084-2014*, sections 4.1 and 7.3. Only those originating in *AUG*, and the ones introduced in this Security Target, are detailed in the following sections.

Table 5. Summary of security objectives

|              | Label                   | Title                                                   |  |

|--------------|-------------------------|---------------------------------------------------------|--|

|              | BSI.O.Leak-Inherent     | Protection against Inherent Information Leakage         |  |

|              | BSI.O.Phys-Probing      | Protection against Physical Probing                     |  |

|              | BSI.O.Malfunction       | Protection against Malfunctions                         |  |

|              | BSI.O.Phys-Manipulation | Protection against Physical Manipulation                |  |

|              | BSI.O.Leak-Forced       | Protection against Forced Information Leakage           |  |

| ш            | BSI.O.Abuse-Func        | Protection against Abuse of Functionality               |  |

| 105          | BSI.O.Identification    | TOE Identification                                      |  |

|              | BSI.O.RND               | Random Numbers                                          |  |

|              | BSI.O.Cap-Avail-Loader  | Capability and Availability of the Loader               |  |

|              | AUG1.O.Add-Functions    | Additional Specific Security Functionality              |  |

|              | AUG4.O.Mem-Access       | Dynamic Area based Memory Access Control                |  |

|              | O.Controlled-ES-Loading | Controlled loading of the Security IC Embedded Software |  |

| nts          | BSI.OE.Resp-Appl        | Treatment of User Data of the Composite TOE             |  |

| nme          | BSI.OE.Process-Sec-IC   | Protection during composite product manufacturing       |  |

| Environments | BSI.OE.Lim-Block-Loader | Limitation of capability and blocking the Loader        |  |

## 4.1 Security objectives for the TOE

BSI.O.Leak-Inherent Protection against Inherent Information Leakage

BSI.O.Phys-Probing Protection against Physical Probing

BSI.O.Malfunction Protection against Malfunctions

BSI.O.Phys-Manipulation Protection against Physical Manipulation

BSI.O.Leak-Forced Protection against Forced Information Leakage

BSI.O.Abuse-Func Protection against Abuse of Functionality

BSI.O.Identification TOE Identification

BSI.O.RND Random Numbers

BSI.O.Cap-Avail-Loader Capability and Availability of the Loader

AUG1.O.Add-Functions Additional Specific Security Functionality:

The TOE must provide the following specific security functionality to the **Security IC** Embedded Software:

- Triple Data Encryption Standard (TDES),

- Advanced Encryption Standard (AES),

- Elliptic Curves Cryptography on GF(p), if Neslib is embedded only,

- Secure Hashing (SHA-1<sup>(1)</sup>, SHA-224, SHA-256, SHA-384, SHA-512), if Neslib is embedded only,

- Rivest-Shamir-Adleman (RSA), if Neslib is embedded only,

- Deterministic Random Bit Generator (DRBG), if Neslib is embedded only,

- Prime Number Generation, if Neslib is embedded only.

- Note that SHA-1 is no longer recommended as a cryptographic function in the context of smart card applications. Hence, Security IC Embedded Software may need to use another SHA to achieve a suitable strength.

AUG4.O.Mem-Access

**Dynamic** Area based Memory Access Control:

The TOE must provide the **Security IC** Embedded Software with the capability to define **dynamic memory segmentation and protection**. The TOE must then enforce **the defined access rules** so that access of software to memory areas is controlled as required, for example, in a multi-application environment.

O.Controlled-ES-Loading

Controlled loading of the Security IC Embedded Software: The TOE must provide the capability to load the Security IC Embedded Software into the NVM, either before TOE delivery, under ST authority, either after TOE delivery, under the composite product manufacturer authority. The TOE must restrict the access to these features. The TOE must provide control means to check the integrity of the loaded user data. This capability is not available in User configuration.

## 4.2 Security objectives for the environment

Security Objectives for the Security IC Embedded Software development environment (phase 1):

BSI.OE.Resp-Appl Treatment of User Data of the Composite TOE

Security Objectives for the operational Environment (phase 4 up to 6):

BSI.OE.Process-Sec-IC Protection during composite product manufacturing BSI.OE.Lim-Block-Loader Limitation of capability and blocking the Loader

## 4.3 Security objectives rationale

- The main line of this rationale is that the inclusion of all the security objectives of the *BSI-CC-PP-0084-2014* protection profile, together with those in *AUG*, and those introduced in this ST, guarantees that all the security environment aspects identified in *Section 3* are addressed by the security objectives stated in this chapter.

- 113 Thus, it is necessary to show that:

- security environment aspects from AUG and from this ST, are addressed by security objectives stated in this chapter,

- security objectives from *AUG* and from this ST, are suitable (i.e. they address security environment aspects),

- security objectives from *AUG* and from this ST, are consistent with the other security objectives stated in this chapter (i.e. no contradictions).

- The selected augmentations from *AUG* introduce the following security environment aspects:

- TOE threat "Memory Access Violation, (AUG4.T.Mem-Access)",

- organisational security policy "Additional Specific Security Functionality, (AUG1.P.Add-Functions)".

- 115 The augmentation made in this ST introduces the following security environment aspects:

- organisational security policy "Controlled loading of the Security IC Embedded Software, (P.Controlled-ES-Loading)".

- The justification of the additional policies, and additional threats, provided in the next subsections shows that they do not contradict to the rationale already given in the protection profile *BSI-CC-PP-0084-2014* for the assumptions, policy and threats defined there.

Table 6. Security Objectives versus Assumptions, Threats or Policies

| Assumption, Threat or<br>Organisational Security Policy | Security Objective                                | Notes                            |

|---------------------------------------------------------|---------------------------------------------------|----------------------------------|

| BSI.A.Resp-Appl                                         | BSI.OE.Resp-Appl                                  | Phase 1                          |

| BSI.P.Process-TOE                                       | BSI.O.Identification                              | Phase 2-3<br>optional<br>Phase 4 |

| BSI.P.Lim_Block_Loader                                  | BSI.O.Cap-Avail-Loader<br>BSI.OE.Lim-Block-Loader | Phase 5-6<br>optional<br>Phase 4 |

Assumption, Threat or **Security Objective** Notes **Organisational Security Policy** BSI.A.Process-Sec-IC BSI.OE.Process-Sec-IC Phase 5-6 optional Phase 4 P.Controlled-ES-Loading Phase 4-6 O.Controlled-ES-Loading AUG1.P.Add-Functions AUG1.O.Add-Functions BSI.T.Leak-Inherent BSI.O.Leak-Inherent BSI.T.Phys-Probing BSI.O.Phys-Probing BSI.T.Malfunction BSI.O.Malfunction BSI.T.Phys-Manipulation BSI.O.Phys-Manipulation BSI.T.Leak-Forced BSI.O.Leak-Forced BSI.T.Abuse-Func BSI.O.Abuse-Func BSI.T.RND BSI.O.RND AUG4.T.Mem-Access AUG4.O.Mem-Access

Table 6. Security Objectives versus Assumptions, Threats or Policies (continued)

## 4.3.1 TOE threat "Memory Access Violation"

- The justification related to the threat "Memory Access Violation, (*AUG4.T.Mem-Access*)" is as follows:

- According to AUG4.O.Mem-Access the TOE must enforce the dynamic memory segmentation and protection so that access of software to memory areas is controlled. Any restrictions are to be defined by the Security IC Embedded Software. Thereby security violations caused by accidental or deliberate access to restricted data (which may include code) can be prevented (refer to AUG4.T.Mem-Access). The threat AUG4.T.Mem-Access is therefore removed if the objective is met.

- The added objective for the TOE *AUG4.O.Mem-Access* does not introduce any contradiction in the security objectives for the TOE.

# 4.3.2 Organisational security policy "Additional Specific Security Functionality"

- The justification related to the organisational security policy "Additional Specific Security Functionality, (*AUG1.P.Add-Functions*)" is as follows:

- Since *AUG1.O.Add-Functions* requires the TOE to implement exactly the same specific security functionality as required by *AUG1.P.Add-Functions*, *and in the very same conditions*, the organisational security policy is covered by the objective.

- Nevertheless the security objectives BSI.O.Leak-Inherent, BSI.O.Phys-Probing, , BSI.O.Malfunction, BSI.O.Phys-Manipulation and BSI.O.Leak-Forced define how to implement the specific security functionality required by AUG1.P.Add-Functions. (Note that these objectives support that the specific security functionality is provided in a secure way as expected from AUG1.P.Add-Functions.) Especially BSI.O.Leak-Inherent and BSI.O.Leak-Forced refer to the protection of confidential data (User Data or TSF data) in

general. User Data are also processed by the specific security functionality required by *AUG1.P.Add-Functions*.

The added objective for the TOE *AUG1.O.Add-Functions* does not introduce any contradiction in the security objectives for the TOE.

# 4.3.3 Organisational security policy "Controlled loading of the Security IC Embedded Software"

- The justification related to the organisational security policy "Controlled loading of the Security IC Embedded Software, (*P.Controlled-ES-Loading*)" is as follows:

- Since O.Controlled-ES-Loading requires the TOE to implement exactly the same specific security functionality as required by P.Controlled-ES-Loading, and in the very same conditions, the organisational security policy is covered by the objective.

- The added objective for the TOE *O.Controlled-ES-Loading* does not introduce any contradiction in the security objectives.

## 5 Security requirements (ASE REQ)

This chapter on security requirements contains a section on security functional requirements (SFRs) for the TOE (Section 5.1), a section on security assurance requirements (SARs) for the TOE (Section 5.2), a section on the refinements of these SARs (Section 5.3) as required by the "BSI-CC-PP-0084-2014" Protection Profile. This chapter includes a section with the security requirements rationale (Section 5.4).

## 5.1 Security functional requirements for the TOE

- Security Functional Requirements (SFRs) from the "BSI-CC-PP-0084-2014" Protection Profile (PP) are drawn from CCMB-2012-09-002 R4, except the following SFRs, that are extensions to CCMB-2012-09-002 R4:

- FCS RNG Generation of random numbers,

- FMT\_LIM Limited capabilities and availability,

- FAU\_SAS Audit data storage,

- FDP\_SDC Stored data confidentiality.

The reader can find their certified definitions in the text of the "BSI-CC-PP-0084-2014" Protection Profile.

- All extensions to the SFRs of the "BSI-CC-PP-0084-2014" Protection Profiles (PPs) are exclusively drawn from CCMB-2012-09-002 R4.

- All <u>iterations</u>, <u>assignments</u>, <u>selections</u>, or <u>refinements</u> on SFRs have been performed according to section C.4 of <u>CCMB-2012-09-001</u> R4. They are easily identified in the following text as they appear **as indicated here**. Note that in order to improve readability, iterations are sometimes expressed within tables.

- In order to ease the definition and the understanding of these security functional requirements, a simplified presentation of the TOE Security Policy (TSP) is given in the following section.

- The selected security functional requirements for the TOE, their respective origin and type are summarized in *Table 7*.

Table 7. Summary of functional security requirements for the TOE

| Label     | Title                                     | Addressing     | Origin                  | Туре            |

|-----------|-------------------------------------------|----------------|-------------------------|-----------------|

| FRU_FLT.2 | Limited fault tolerance                   | LIVISITUDOTION | BSI-CC-PP-<br>0084-2014 | CCMB-20         |

| FPT_FLS.1 | Failure with preservation of secure state |                |                         | .2012-09-002 R4 |

Table 7. Summary of functional security requirements for the TOE (continued)

| Label                                        | Title                                       | Addressing                                   | Origin                              | Туре                         |  |

|----------------------------------------------|---------------------------------------------|----------------------------------------------|-------------------------------------|------------------------------|--|

| FMT_LIM.1 / Test                             | Limited capabilities                        | Abuse of TEST                                | BSI-CC-PP-                          | Extended CCMB-2012-09-002 R4 |  |

| FMT_LIM.2 / Test                             | Limited availability                        | functionality                                | 0084-2014                           |                              |  |

| FMT_LIM.1 /<br>Loader                        | Limited capabilities                        | Abuse of Loader                              |                                     |                              |  |

| FMT_LIM.2 /<br>Loader                        | Limited availability                        | functionality                                | BSI-CC-PP-                          |                              |  |

| FAU_SAS.1                                    | Audit storage                               | Lack of TOE identification                   | 0084-2014<br>Operated               |                              |  |

| FDP_SDC.1                                    | Stored data confidentiality                 |                                              | _                                   |                              |  |

| FDP_SDI.2                                    | Stored data integrity monitoring and action | Physical manipulation & probing              |                                     |                              |  |

| FPT_PHP.3                                    | Resistance to physical attack               | 1,5,55,113                                   |                                     |                              |  |

| FDP_ITT.1                                    | Basic internal transfer protection          |                                              | BSI-CC-PP-                          |                              |  |

| FPT_ITT.1                                    | Basic internal TSF data transfer protection | Leakage                                      | 0084-2014                           |                              |  |

| FDP_IFC.1                                    | Subset information flow control             |                                              |                                     |                              |  |

| FCS_RNG.1                                    | Random number generation                    | Weak cryptographic quality of random numbers | BSI-CC-PP-<br>0084-2014<br>Operated | Extended                     |  |

| FCS_COP.1                                    | Cryptographic operation                     |                                              | AUG #1<br>Operated                  |                              |  |

| FCS_CKM.1<br>(if Neslib is<br>embedded only) | Cryptographic key generation                | Cipher scheme support                        | Security Target<br>Operated         | CC                           |  |

| FDP_ACC.2 /<br>Memories                      | Complete access control                     | Mamary access violation                      | Security Target<br>Operated         | :MB-20                       |  |

| FDP_ACF.1 /<br>Memories                      | Security attribute based access control     | Memory access violation                      |                                     | 012-09-                      |  |

| FMT_MSA.3 /<br>Memories                      | Static attribute initialisation             | AUG #4<br>Operated                           |                                     | CCMB-2012-09-002 R4          |  |

| FMT_MSA.1 /<br>Memories                      | Management of security attribute            | Correct operation                            |                                     | 74                           |  |

| FMT_SMF.1 /<br>Memories                      | Specification of management functions       | Security Target<br>Operated                  |                                     |                              |  |

Label Title Addressing Origin Type FDP ITC.1/ Import of user data User data loading access Loader without security attributes violation FDP ACC.1/ Subset access control Loader FDP ACF.1/ Security attribute based CCMB-2012-09-002 R4 Loader access control FMT MSA.3/ Static attribute Correct operation Loader initialisation Security Target Operated FMT MSA.1/ Management of security Loader attribute FMT SMR.1/ Security roles Abuse of ADMIN Loader functionality FIA UID.1/ Timing of identification Loader FMT\_SMF.1/ Specification of Loader management functions

Table 7. Summary of functional security requirements for the TOE (continued)

## 5.1.1 Security Functional Requirements from the Protection Profile

## Limited fault tolerance (FRU\_FLT.2)

The TSF shall ensure the operation of all the TOE's capabilities when the following failures occur: exposure to operating conditions which are not detected according to the requirement Failure with preservation of secure state (FPT FLS.1).

#### Failure with preservation of secure state (FPT\_FLS.1)

The TSF shall preserve a secure state when the following types of failures occur: **exposure** to operating conditions which may not be tolerated according to the requirement Limited fault tolerance (FRU FLT.2) and where therefore a malfunction could occur.

#### 135 Refinements:

The term "failure" above also covers "circumstances". The TOE prevents failures for the "circumstances" defined above.

Regarding application note 14 of BSI-CC-PP-0084-2014, the secure state is reached by an immediate interrupt or by a reset, depending on the current context.

Regarding application note 15 of BSI-CC-PP-0084-2014, the TOE provides information on the operating conditions monitored during Security IC Embedded Software execution and after a warm reset. No audit requirement is however selected in this Security Target.

#### Limited capabilities (FMT LIM.1) / Test

The TSF shall be designed and implemented in a manner that limits their capabilities so that in conjunction with "Limited availability (FMT\_LIM.2)" the following policy is enforced:

\*Limited capability and availability Policy / Test.

## Limited availability (FMT\_LIM.2) / Test

- The TSF shall be designed and implemented in a manner that limits their availability so that in conjunction with "Limited capabilities (FMT\_LIM.1) / Test" the following policy is enforced: Limited capability and availability Policy / Test.

- 138 SFP 1: Limited capability and availability Policy / Test

Deploying Test Features after TOE Delivery does not allow User Data of the Composite TOE to be disclosed or manipulated, TSF data to be disclosed or manipulated, software to be reconstructed and no substantial information about construction of TSF to be gathered which may enable other attacks.

## Audit storage (FAU\_SAS.1)

The TSF shall provide the test process before TOE Delivery with the capability to store the Initialisation Data and/or Pre-personalisation Data and/or supplements of the Security IC Embedded Software in the NVM.

## Stored data confidentiality (FDP\_SDC.1)

The TSF shall ensure the confidentiality of the information of the user data while it is stored in *all the memory areas where it can be stored*.

#### Stored data integrity monitoring and action (FDP SDI.2)

- The TSF shall monitor user data stored in containers controlled by the TSF for integrity errors on all objects, based on the following attributes: user data stored in all possible memory areas, depending on the integrity control attributes.

- Upon detection of a data integrity error, the TSF shall *signal the error and react*.

#### Resistance to physical attack (FPT PHP.3)

The TSF shall resist *physical manipulation and physical probing,* to the *TSF* by responding automatically such that the SFRs are always enforced.

#### 144 Refinement:

The TSF will implement appropriate mechanisms to continuously counter physical manipulation and physical probing. Due to the nature of these attacks (especially manipulation) the TSF can by no means detect attacks on all of its elements. Therefore, permanent protection against these attacks is required ensuring that security functional requirements are enforced. Hence, "automatic response" means here (i)assuming that there might be an attack at any time and (ii)countermeasures are provided at any time.

## Basic internal transfer protection (FDP\_ITT.1)

The TSF shall enforce the **Data Processing Policy** to prevent the **disclosure** of user data when it is transmitted between physically-separated parts of the TOE.

#### Basic internal TSF data transfer protection (FPT\_ITT.1)

- The TSF shall protect TSF data from *disclosure* when it is transmitted between separate parts of the TOE.

- 147 Refinement:

The different memories, the CPU and other functional units of the TOE (e.g. a cryptographic co-processor) are seen as separated parts of the TOE.

This requirement is equivalent to FDP\_ITT.1 above but refers to TSF data instead of User Data. Therefore, it should be understood as to refer to the same Data Processing Policy defined under FDP\_IFC.1 below.

## Subset information flow control (FDP\_IFC.1)

The TSF shall enforce the **Data Processing Policy** on **all confidential data when they are**processed or transferred by the TOE or by the Security IC Embedded Software.

#### 149 SFP 2: Data Processing Policy

User Data of the Composite TOE and TSF data shall not be accessible from the TOE except when the Security IC Embedded Software decides to communicate the User Data via an external interface. The protection shall be applied to confidential data only but without the distinction of attributes controlled by the Security IC Embedded Software.

## Random number generation (FCS\_RNG.1)

The TSF shall provide a *physical* random number generator that implements:

- A total failure test detects a total failure of entropy source immediately when the RNG has started. When a total failure is detected, no random numbers will be output.

- If a total failure of the entropy source occurs while the RNG is being operated, the RNG prevents the output of any internal random number that depends on some raw random numbers that have been generated after the total failure of the entropy source.

- The online test shall detect non-tolerable statistical defects of the raw random number sequence (i) immediately when the RNG has started, and (ii) while the RNG is being operated. The TSF must not output any random numbers before the power-up online test has finished successfully or when a defect has been detected.

- The online test procedure shall be effective to detect non-tolerable weaknesses

of the random numbers soon.

- The online test procedure checks the quality of the raw random number sequence. It is triggered externally. The online test is suitable for detecting non-tolerable statistical defects of the statistical properties of the raw random numbers within an acceptable period of time.

- 151 The TSF shall provide octets of bits that meet

- Test procedure A does not distinguish the internal random numbers from output sequences of an ideal RNG.

- The average Shannon entropy per internal random bit exceeds 0.997.

# 5.1.2 Additional Security Functional Requirements for the cryptographic services

## Cryptographic operation (FCS\_COP.1)

The TSF shall perform *the operations in Table 8* in accordance with a specified cryptographic algorithm *in Table 8* and cryptographic key sizes *of Table 8* that meet the

standards in Table 8. The list of operations depends on the presence of Neslib, as indicated in Table 8 (Restrict).

Table 8. FCS\_COP.1 iterations (cryptographic operations)